패리티 비트 & 해밍 코드

패리티 비트 (Parity Bit)

정보 전달 과정에서 오류가 생겼는지 검사하기 위해 추가하는 비트 → 오류 검출

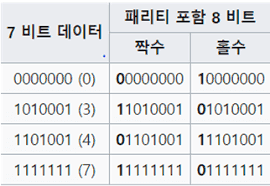

1바이트(8비트) 구조에서 패리티 비트는 7비트 크기의 ASCII 코드를 제외한 나머지 1비트이다.

짝수 패리티

→ 데이터의 모든 1의 개수를 짝수로 맞춘다

홀수 패리티

→ 데이터의 모든 1의 개수를 홀수로 맞춘다

특징

- 2개의 bit 데이터가 손실되면 알아차릴 수 없다.

- 오류 검출만 할 뿐 수정하지는 않는다.

해밍 코드 (Hamming Code)

데이터 전송 시, 1비트의 오류를 정정할 수 있는 자기 오류정정 코드 → 오류 정정

패리티 비트를 보고, 1비트에 대한 오류를 정정할 곳을 찾아 수정할 수 있다.

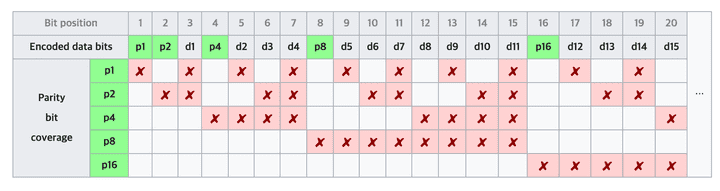

생성 규칙

- d: 데이터 비트 수

-

p: 패리티 비트 수

- 2^p ≥ d + p + 1 를 만족하는 p의 최소 값

짝수 패리티의 해밍 코드가 0011011일때, 오류 수정

- d: 4, p: 3

- 2의 n승 번째 자리인 1, 2, 4번째 자릿수가 패리티 비트

p1 ⇒ 1, 3, 5, 7번째 비트 확인 : 0101로 짝수이므로 '**0**' p2 ⇒ 2, 3, 6, 7번째 비트 확인 : 0111로 홀수이므로 '**1**' p3 ⇒ 4, 5, 6, 7번째 비트 확인 : 1011로 홀수이므로 '**1**'역순으로 패리티비트 ‘110’을 10진법으로 바꾸면 ‘6’이므로 6번째 비트를 수정하면 된다.

따라서 수정한 데이터는 0011001이다.